摘要:在研究时序电路设计的基础上,针对一具体序列信号,提出了用不同功能的MSI芯片对同一信号进行设计的思路。文中详细阐述了用移位寄存器及必要的门电路设计序列信号发生器的过程。实验证明,用这几种方法构成的序列信号发生器,不但电路简捷,连接方便,而且工作可靠。

论文关键词:设计,序列信号发生器,计数器,数据选择器,移位寄存器

在数字信号的传输和数字系统的测试中,常常用到一组特定的串行数字信号,通常把这种串行数字信号叫序列信号。而把产生序列信号的电路称为序列信号发生器。

在较旧版本的数字电子技术的教材中,并未涉及到有关序列信号发生器的概念和设计方法的讲述。在新版教材的有关章节中,虽然增加了该内容但讲解并不深入,并且在该章节的目录中注有“*”号,表示该部分内容是建议作为选讲的内容,在学时较少或要求不高的情况下,建议首先删减的内容。因此,很多同学对该部分内容较为生疏。但在实践教学中已将序列信号发生器的设计放在了选做的内容,由于上述原因致使该部分选内容未落在实处。

随着数字电子技术的进步,尤其是集成电路的迅猛发展,采用中规模集成电路(MSI)芯片构成序列信号发生器已非常方便简洁。设计序列信号发生器的方法有很多种,比较简单直观的方法是用计数器和数据选择器组成,也可以用计数器和必要的组合逻辑电路构成,当然用移位寄存器和必要的门电路也是组成序列信号发生器的方法之一。

1 用计数器和数据选择器构成序列信号发生器

设计过程一般可分以下几步进行。首先,根据序列信号长度M设计模为M的计数器,计数器状态可以自定。然后根据计数器状态转换关系和序列信号要求,选择和设计数据选择器的输入信号,并确定其地址输入端与计数器输出端的连接方式。最后,根据计数器和数据选择器的功能表以及设计结果画出逻辑电路图。

例如,设计一个产生01011序列信号的序列信号发生器,由于所需信号的循环长度为五,首先可选用一片MSI的十进制计数器,通过选取适当的反馈清零信号得到一个五进制计数器,将其输出端信号接入另一片八选一数据选择器的地址输入端,根据数据选择器的逻辑功能可知,只要将其数据输入端接入与序列信号相应的电平,在其原码输出端即可得到所需序列信号。

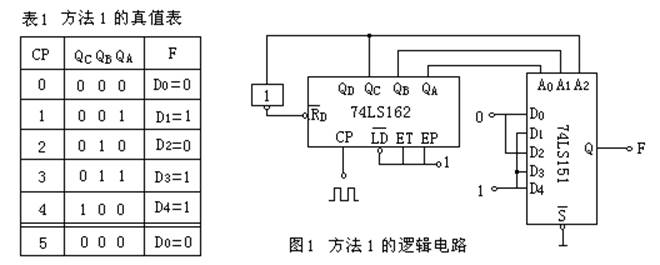

如果选用具有同步清零的十进制计数器74LS162,并选用常用的前五个状态000~100构成五进制,数据选择器选用74LS151,并从其原码输出端得到序列信号,其真值表如表1所示。

根据真值表可知,只要将五进制计数器的输出QCQBQA接入74LS151的地址输入端A2A1A0,将其数据输入端接成D0=D2=0, D1=D3=D4=1,既可从74LS151的Q端得到所需序列信号,逻辑电路如图1所示。

2 用移位寄存器和必要的门电路构成序列信号发生器

设计过程可分以下几步进行(依然以产生01011序列信号为例):

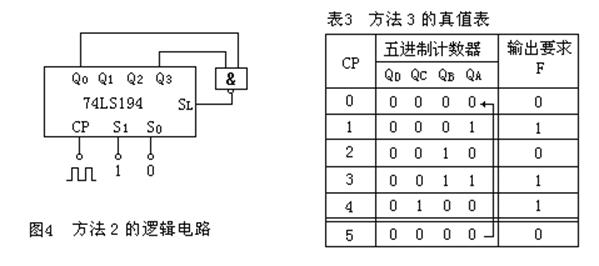

首先,根据给定序列信号的循环长度M,确定所需移位寄存器位数N。其中2n-1> M ≤ 2 n,由于序列信号01011为五位,所以M=5,可取n=3。第二步,要确定移位寄存器的M个独立状态。若取n=3,可将给定的序列信号01011按移位规律三位一组画出五个状态, 可得010,101,011,110,101,由于所得五个状态中有两个重复(101),即不是五个独立状态,此时应增大移位寄存器位数n,若取n=4,按上述方法重新画出五个状态,可得0101,1011,0110,1101,1010,得到五个独立状态,因此确定取n=4,用一片双向移位寄存器74LS194即可。第三步,根据五个不同状态列出移位寄存器的状态转换图及每一个状态所需要的移位输入,即反馈输入信号,列出反馈函数表如表2所示。从表中所知,移位寄存器只需进行左移操作,因此反馈函数F=SL.。根据反馈函数表画出F的卡诺图如图2所示。根据卡诺图得出F(SL)= 可得010,101,011,110,101,由于所得五个状态中有两个重复(101),即不是五个独立状态,此时应增大移位寄存器位数n,若取n=4,按上述方法重新画出五个状态,可得0101,1011,0110,1101,1010,得到五个独立状态,因此确定取n=4,用一片双向移位寄存器74LS194即可。第三步,根据五个不同状态列出移位寄存器的状态转换图及每一个状态所需要的移位输入,即反馈输入信号,列出反馈函数表如表2所示。从表中所知,移位寄存器只需进行左移操作,因此反馈函数F=SL.。根据反馈函数表画出F的卡诺图如图2所示。根据卡诺图得出F(SL)= 。 。

若令74LS194的控制方式选择端S1S2=10,左移串行输入端SL= ,则可由74LS194的任一输出端得到01011序列信号(只是起始位不同)。 ,则可由74LS194的任一输出端得到01011序列信号(只是起始位不同)。

在完成了上述设计后,需要检查系统是否能自启动。即检查当741LS194的输出端Q0~Q3出现无效状态时,根据F(SL)

= 观察其能否在若干个时钟脉冲作用下进入有效循环。其完全状态图如图3所示。由图3可知,该电路能够自启动。 观察其能否在若干个时钟脉冲作用下进入有效循环。其完全状态图如图3所示。由图3可知,该电路能够自启动。

最后一步,画出逻辑电路。根据所用双向移位寄存器的功能表以及所设计反馈函数的F(SL)= 可画出其逻辑电路如图4所示。 可画出其逻辑电路如图4所示。

3 用计数器和必要的组合逻辑电路构成序列信号发生器

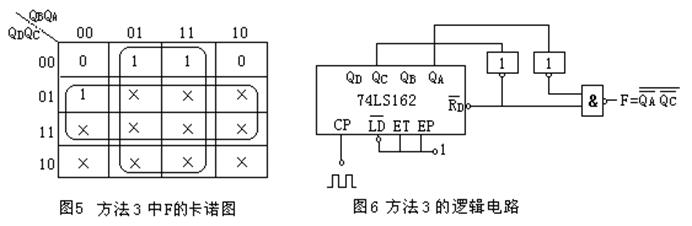

设计思路与上两种方法近似,由于要构成的序列信号01011是一个五位的串行数字信号,可选用74LS162首先构成一个五进制计数器,再通过一定的组合逻辑电路使其输出F=01011即可。根据题义可列真值表如表3所示。

根据真值表作出反馈函数F的卡诺图如图5所示。化简得出F=QA+QC= ,因此可得出如图6所示逻辑电路。 ,因此可得出如图6所示逻辑电路。

注意,采用MSI设计电路时,必须给器件的所有控制端提供必要的信号,使之能够正常工作。如74LS162的ET、EP引脚以及74LS151的 端引脚等。 端引脚等。

实验证明,用以上几种方法构成的序列信号发生器不但电路简捷,连接方便,而且工作可靠。总之,在时序电路的设计过程中,根据实际设计要求,可以有多种不同的设计思路和方案选择,而针对同一题目采用不同方案进行设计则对开拓学习思路,掌握时序电路设计方法,提高学生对设计过程的理性认识有很大的促进作用。

The Methods of Designing Sequence signal generator with MSI

HI Bihua

(EEEC_Shaanxi University of Technology Hanzhong 723003 in China)

Abstract: The article that based on the investigating of the sequence circuits, questioned about the design methods that using various functional MSI chip to produce the same signal. At first, the paper described the process that using the shift register and the necessary gate circuit to design the Sequence Signal Generator in detail. Then according to the experiment, it proved that the methods used not only simple but also easy to connect, and the circuit could worked reliable.

Keywords: Design Sequence signal generator Counter Data-selector Shift- register

参考文献

[1]阎石主编数字电子技术基础清华大学出版社 1998

[2]杨颂华数字电子技术基础西安电子科技大学出版社 2000

[3]罗朝杰数字逻辑设计基础人民邮电出版社 1982

[4]王毓银数字电路逻辑设计高等教育出版社 1999

|