论文摘要:探讨了一种运用SoPC技术,将Nios系统、DDS信号产生电路、等精度频率计电路嵌入到一块FPGA里,实现信号源的方案。由于FPGA可重配置的特性,信号源可以根据需要随时对主要功能进行修改,不必更换硬件。该信号源功能多,使用范围宽,精度高。系统的主要功能都在一块芯片上,抗干扰能力强,功耗低,体积小。

论文关键词:等精度频率计,信号源

1.引言

信号源是电子系统设计、测试和实验中必备的工具。数字化的信号源转换速度快,具有较高的频率分辨率,频率转换时间和相位连续,相对传统的模拟信号源有更多的优势。实际应用系统中情况各不相同,专用信号源使用范围有限,不改变硬件电路但可以改变信号源功能和使用范围的新型信号源就有了需求。SoPC(SystemOnaProgrammableChip)能够根据需要裁减或扩充功能,加上FPGA(FieldProgrammableGateArray)

可重构的特点,可以满足上述要求。SoPC是采用Nios可配置软核处理器和IP(IntellectualProperty)核在集成电路内搭建的系统,Nios负责系统控制和通

讯,利用现有IP或者HDL语言实现其它主要的硬件部分。该系统在一片FPGA上不仅嵌入了Nios软核MPU,还集成了DDS(DirectDigitalFrequencySynthesis)信号产生电路和等精度频率计,设计方式灵活、可靠性高,功能齐全,功耗比较低,适用于诸多领域。

2.系统总体设计和工作原理

多功能信号源组成如图1所示。SoPC主要由下面几个部分组成,Nios、AvalonBus、BootROM、Timer、外部接口、DDS信号产生电路、等精度频率计、通信、显示和键盘管理。这里,我们着重对Nios的作用、DDS信号产生电路、等精度频率计进行了说明。

图1Nios系统组成图 图1Nios系统组成图

2.1Nios软核

Nios是Altera公司的用户可配置嵌入式32位MPU软核,主要完成系统的管理、控制和人机对话。如DDS中频率、相位、幅度的设置和步进,等精度频率计的键盘模块、数码显示模块的控制与管理。

2.2DDS信号产生电路

DDS用来产生频率、相位和幅度可变的正弦波。DDS的工作原理是利用正弦信号的相位与时间呈线性关系的特性,采用相位累加方法作为地址,读出相应ROM中的值,得到正弦信号的瞬时幅值,实现频率合成。DDS包括频率控制字、相位控制字、同步寄存器、相位累加器、波形存储器、数模转换器、低通滤波器,见图2所示。

图2DDS原理图 图2DDS原理图

在系统时钟的控制下,相位累加器对频率控制字K进行累加,得到相位码,相位码寻址ROM得到幅值码,经过数模转换后得到相应的阶梯波,再经过低通滤波得到连续平滑的由频率控制字K决定的模拟输出波形,输出频率f 为: 为:

f =K·f =K·f /2 /2

设K=1时,DDS最小分辨率是:

f =f =f /2 /2

式中K是频率控制字,N是相位寄存器字长,输出频率是由K和N决定的。DDS可以用来作多波形发生器,只要改变ROM中的数据,预先设置成正弦波、三角波、方波等,根据查表就可以实现不同的波形。利用DSPBuilder设计DDS,然后转换成VHDL,DDS输出波形见图3所示。DDS的分辨率在相位累加器的位数N足够大时,理论上可以获得相应的分辨精度。DDS是一个全数字结构的开环系统,无反馈环节,速度非常快。DDS的相位误差主要依赖于时钟的相位特性,相位误差小,相位是连续变化的,形成的信号具有良好的频谱,这是传统的直接频率合成方法无法实现的。相位字输入的数据宽度M往往小于相位寄存器字长N,实际的DDS结构中N很大,M太大会导致ROM容量的成倍上升,而输出精度受D/A位数的限制未有很大改善,所以我们取N的高M位寻址ROM,这样也出现了截断误差。

图3DDS输出波形 图3DDS输出波形

2.3等精度频率计

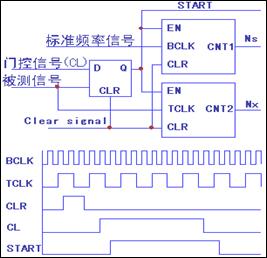

电子测量领域经常要检测频率,测量频率的方法也各式各样。传统测频原理的频率计测量精度将随被测信号频率的下降而降低,即测量精度随被测信号的频率的变化而变化,在实用中有较大的局限性,而等精度频率计不但具有较高的测量精度,且在整个频率区域能保持恒定的测试精度。等精度频率计的前一级是信号整形电路,用于对待测信号进行放大和整形,作为输入信号。测频电路是频率计的核心电路模块,系统时钟作为标准频率信号。控制测频操作和读取测频数据,并对相应数据作处理的任务由Nios完成。等精度测频原理图见图4所示。

图4等精度频率计结构和波形图

CNT1和CNT2是两个可控的32位计数器,EN是它们的计数允许端,高电平有效。标准频率信号从CNT1的时钟端BCLK输入,设其频率为Fs,被测信号从CNT2的时钟端TCLK输入,令其频率为Fx。使CLR清零,同时两个计数器和D触发器被置0,D触发器的Q端也为0,禁止两个计数器计数。预置门控信号CL由Nios发出,它的宽度是可以控制的,取0.01-1S某一值时,对测频的精度影响较小。CL为高电平,D触发器输出要到被测信号TCLK的上升沿通过才为1,这时START也为1,计数器CNT1和CNT2工作,分别同时对标准时钟和被测信号计数。CL为0时,两个计数器还没有停止工作,直到下一个被测信号的上升沿到来时,D触发器输出变为0,两个计数器同时被关闭。 1/2 1 2 下一页 尾页 |